层次化的设计方法(全加器设计)

一、实验原理

对于复杂的电路,有必要采用模块的形式进行设计。将不同的逻辑功能用相应的模块实现。当设计出现问题时,可有针对性地对这些模块进行分析。而对那些在设计中重复出现的功能块采用模块的设计方法则可提高效率。

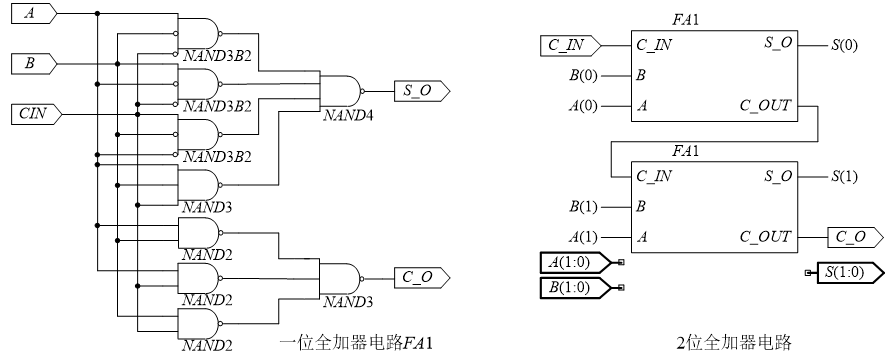

在ISE软件中,顶层采用电原理图方式时允许建立模块,这种方法称为层次化设计。对于复杂系统在采用层次化的设计方法时,各逻辑功能块用宏单元实现。在顶层的逻辑图中将这些宏单元用网线相互连接,而在下层宏单元采用电原理图、硬件描述语言方法描述具体的逻辑。如下层的逻辑较复杂,则可进一步采用层次化的设计方法,即用电原理图的方法描述该层逻辑,而在此层中再用更低层次的宏单元来实现。

(一)由电路原理图产生宏单元模块

可以在设计流程中的设计编辑部分直接选择电原理图,对逻辑进行描述,然后在工具子菜单中选择“Symbol Wizard”,此时可按设计向导将该设计文件转换为宏单元模块,此模块自动将加入到项目库中,通过调用库可将此宏单元调出并安放在原理图中恰当的位置。

(二)宏单元的打开与修改

在电路设计过程中,有需要对电路进行编辑与修改。在顶层电路中可以打开下层宏单元,并进行编辑。设计项目中如有宏单元模块被修改,ISE则会对整个设计项目进行宏单元自动更新。可以采取从项目文件组织结构、从顶层电路原理图等二种方法中的一种打开下层宏单元。

二、实验内容

(一)用层次化的方法设计4位加法器电路

输入数据信号为A3~A0、B3~B0,(A3、B3为最高位),输入的进位信号为CIN,输出数据信号为S3~S0,输出的进位信号为CO。

1、在顶层定义一个4位加法器的宏单元,此加法器在下一层用4个一位的全加器宏单元电路串联实现。

2、设计一套数据对上述电路进行功能验证。

(二)用已验证的4位加法器宏单元组成一个8位的加减器

输入数据信号A7~A0为一个加数或被减数,B7~B0为另一个加数或减数,输入控制信号AS=0时执行加法运算,AS=1时执行减法运算,输出数据信号为D7~D0,输出的进位/借位信号为CO。

1、在顶层用4位加法器宏单元构成8位的加减器。

2、设计一套数据对上述电路进行功能验证。

2018 © 复旦大学电子信息教学实验中心

技术支持: 维程互联

loading......

loading......