迭代设计法(4位全加器与数据比较器的设计)

一、实验原理

实验四设计的4位加法器采用4个1位的全加器串接而成,采用了迭代设计法,迭代设计法的主要思路是:在一个设计中,如存在多个重复的单元,则找出这些单元串联的规律,然后设计其中的一个单元,将这些单元按要求串接成所需的电路。

因此在设计可迭代的单元时,必然包含负责实现本单元主要功能的主输入和主输出,还包含负责单元之间信息传递的辅助输入和辅助输出。如一位的全加器单元中主输入信号为加数Ai、Bi,辅助输入信号为进位输入Ci-1,主输出为和Si,辅助输出为进位输出Ci。

在将多个一位的全加器串接成多位加法器时形成了进位信号的串接,因此后级的运算必须在前级的进位输出形成后才能进行,使系统的运算速度变慢。为改善加法器的运算速度,可将串行的进位运算改为并行运算,即采用超前进位技术。

二、实验内容

(一)设计采用超前进位技术的4位加法器

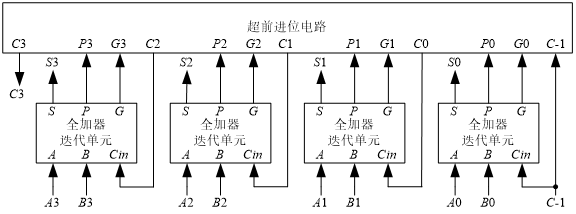

1、在顶层建立一位具有进位产生和传播信号的全加器迭代单元和4位超前进位电路的宏单元,一位全加器迭代单元的输入信号为A、B、Cin,输出信号为S、P、G,4位超前进位电路的输入信号为进位输入C-1,进位产生和传播信号P0~P3、G0~G3,输出信号为C0~C3。验证建立的宏单元的功能。

2、采用上述宏单元构成4位加法器。

3、设计一套数据对上述电路进行功能验证。

(二)采用迭代的方法设计一个4位的数据比较器

输入信号为A3~A0、B3~B0,输出信号为A>B,A=B,A<B。先设计一个2位数据比较器的迭代单元,再利用此单元构成4位数据比较器单元。

1、列出2位数据比较器迭代单元的主输入和主输出信号以及辅助输入和辅助输出信号,在顶层建立2位数据比较器迭代单元的宏单元并验证设计的正确性。

2、利用上述设计的2位数据比较器的迭代单元构成4位数据比较器,并验证设计的正确性。

2018 © 复旦大学电子信息教学实验中心

技术支持: 维程互联

loading......

loading......